芯觀點──聚焦國內外產(chǎn)業(yè)大事件,匯聚中外名人專家觀點,剖析行業(yè)發(fā)展動態(tài),帶你讀懂未來趨勢!

集微網(wǎng)消息,在半導體全產(chǎn)業(yè)鏈中,晶圓制造一直發(fā)揮著基礎核心作用。目前,隨著5G、人工智能和物聯(lián)網(wǎng)等技術不斷發(fā)展,各行各業(yè)對芯片性能和能效要求越來越高。而推動工藝技術發(fā)展的方式主要有兩種,一個是芯片尺寸縮微縮,一個是硅片直徑增大。由于硅片直徑增大涉及整條生產(chǎn)線設備更換,制造工藝精進微縮當前仍是芯片性能持續(xù)提升的主要驅動力。

無論如何,只要摩爾定律還存在,半導體巨頭勢必會搶占先進工藝制高點,其中包括臺積電宣布2022年將支出近300億美元用于2納米、3納米等工藝研發(fā);去年三星宣布2022年量產(chǎn)3納米,2025年量產(chǎn)2納米;英特爾計劃通過2納米制程重回巔峰;而IBM展示的2納米制程也著實驚艷了一小陣。同時,歐洲與日本政府及企業(yè)也寄望通過2納米重振芯片制造。

無疑,全球2納米芯片制程之戰(zhàn)的號角已經(jīng)吹響。但在這場競逐中,各企業(yè)仍主要有“四道坎”需要邁過,包括架構技術、材料、設備和成本。其中,從目前各大廠公布的技術來看,GAAFET全柵場效應晶體管技術將會成為2納米芯片研制的主流工藝。而二維材料和一維材料有望成為突破2納米制程研發(fā)的潛力材料。此外,滿足2納米研發(fā)的光刻機需要2023年開放測試。

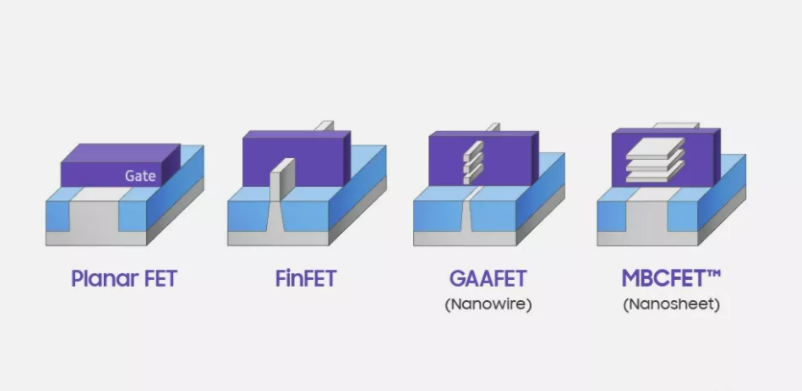

半導體工藝制程晶體管架構示意圖

臺積電、三星“雙雄對決”

作為先進工藝的主力推動者,臺積電近年來一直引領行業(yè)發(fā)展,其中包括2018年推出7納米,2020年推出5納米,2022年將如期推出3納米,同時2納米工藝也在推進研發(fā),預計最快2024年投產(chǎn)。官方資料顯示,與5納米工藝相比,臺積電3納米的晶體管密度達到每平方毫米2.5億個,在邏輯密度上提升1.7倍,性能提升11%,同等性能下功耗可降低25%-30%。

為了減少生產(chǎn)工具以及客戶設計的變更,臺積電的3納米將會沿用鰭式場效應晶體管(FinFET)架構。但隨著工藝節(jié)點發(fā)展到3納米后,晶體管溝道進一步縮短,F(xiàn)inFET結構將遭遇量子隧穿效應的限制。因此,臺積電據(jù)將在2納米芯片中采用類似全柵場效應晶體管(GAAFET)結構。可以說,這一架構是FinFET技術升級版,將能進一步提升柵極對溝道電流的控制能力。

顯然,2納米在技術上革新非常關鍵。根據(jù)國際器件和系統(tǒng)路線圖(IRDS)規(guī)劃,在2021-2022年以后,F(xiàn)inFET結構將逐步被GAAFET結構所取代。該架構即通過更大的閘極接觸面積提升對電晶體導電通道的控制能力,從而降低操作電壓、減少疏漏電流,有效降低芯片運算功耗與操作溫度。比如GAAFET技術將溝道四側全部包裹,F(xiàn)inFET的柵極僅包裹溝道三側。

為了在先進工藝制程上對臺積電彎道超車,三星不僅調整了芯片工藝路線圖,而且在技術架構上大膽革新,其中包括跳過4納米工藝,由5納米直接升至3納米,而且3納米、2納米工藝都將使用GAAFET技術。2021年10月,三星宣布3納米芯片已開始成功流片,將于2022年上半年生產(chǎn),第二代3納米芯片預計于2023年開始生產(chǎn),2納米芯片將于2025年量產(chǎn)。

按照規(guī)劃,三星的3納米GAAFET工藝將采用多橋式-溝道場效應晶體管(MBCFET)晶體管結構。與當前的5納米工藝相比,其面積減少35%,性能提高30%,同時功耗降低了50%。此外,在IEDM 2021國際電子元件大會上,三星還攜手IBM宣布了一種名為垂直傳輸場效應晶體管 (VTFET) 的芯片設計技術,并表示該技術突破了目前1納米工藝設計的瓶頸。

盡管在GAAFET架構的開發(fā)時程上落后于三星,但臺積電在FinFET技術領域具備深厚底蘊,從而將大大縮短由3納米FinFET切換至2納米該技術的周期。按照以往經(jīng)驗,三星在晶體管參數(shù)、芯片功耗、發(fā)熱問題、良品率等性能上都比臺積電略遜一籌。此外,作為純晶圓代工企業(yè),臺積電還歷來獲得了龐大客戶群支持。因此,三星的彎道超車夢或依然艱難。

英特爾、IBM“搖旗吶喊”

在經(jīng)歷了先進制程持續(xù)“擠牙膏”,移動互聯(lián)網(wǎng)時代“被超越”以及傳統(tǒng)PC市場“被蠶食”后,英特爾希望通過一系列戰(zhàn)略舉措,重新奪回半導體行業(yè)領頭羊的地位。而制造能力強化正是其中關鍵一環(huán)。1月22日,英特爾宣布一項新的投資計劃,將在美國俄亥俄州投資200億美元建設兩座半導體制造工廠,2025年建成時將使用全球最先進工藝制造芯片產(chǎn)品。

此前,2021年7月,英特爾曾公布了最新的技術路線,并對重要工藝命名進行了修改:10納米技術改名Intel 7,7納米技術改為Intel4,5納米技術改成Intel 3,2納米技術改成Intel20A。其中,Intel 3在2023年下半年量產(chǎn),Intel 20A在2024年量產(chǎn),Intel18A工藝將于2025年推出。而在2納米節(jié)點時,英特爾將由FinFET工藝轉向其稱為RibbonFET的GAAFET晶體管。

由于先進制程落后競爭對手約一代,英特爾似乎意識到了嚴峻危機,開始到處求合作,其中包括與三星、IBM簽署協(xié)議共同研發(fā)2納米工藝,不久后又傳出與臺積電合作3納米制程測試。同時,英特爾還在先進工藝研發(fā)和制造上大舉投資,預計最終將投資達1000億美元,共建設8家制造工廠。基于此,英特爾未來或將與臺積電、三星在先進工藝上展開尖峰對決。

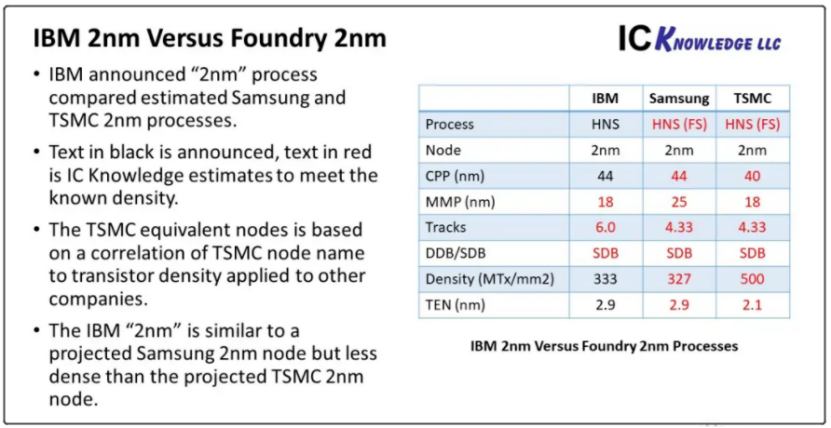

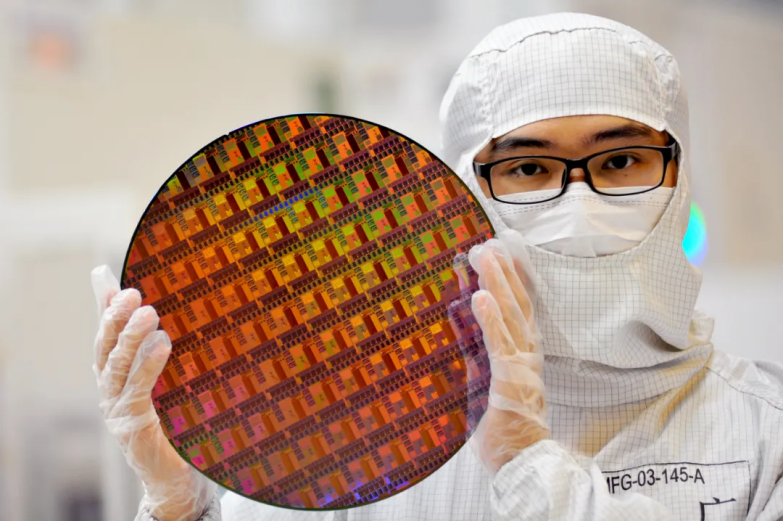

在半導體領域,IBM可謂也是先進工藝制程創(chuàng)新的佼佼者,曾經(jīng)率先推出7納米、5納米乃至2納米工藝。2021年5月,IBM發(fā)布了全球首個2納米制造工藝,并在美國紐約州奧爾巴尼的工廠展示了2納米工藝生產(chǎn)的完整300mm晶圓。據(jù)預計,IBM 2納米工藝或能在每平方毫米芯片上集成3.33億個晶體管,遠高于臺積電5納米工藝的每平方毫米約1.71億個晶體管。

IBM當時宣稱,與最先進的7納米節(jié)點芯片相比,這項技術預計可使芯片的性能提升45%,能耗降低75%,并能助力手機、數(shù)據(jù)中心、PC、自動駕駛等領域應用實現(xiàn)性能飛躍。具體而言,2納米芯片將加快PC、手機應用程序的處理速度,更快速地接入互聯(lián)網(wǎng),以及助力自動駕駛算法更快運行。此外,數(shù)據(jù)中心能耗巨大,如將處理器替換為2納米產(chǎn)品將可大大降低等。

不過,雖然同樣采用了GAAFET工藝,但該技術目前仍處在概念驗證階段,與量產(chǎn)工藝差距較大。通常,芯片工藝從實驗室研發(fā)到正式量產(chǎn)商用,還需要代工廠不斷提升晶圓良率。而即便解決晶圓良率問題,IBM當前也已不具備大規(guī)模量產(chǎn)芯片的能力。此前,IBM曾與三星、英特爾簽署了聯(lián)合研制2納米的協(xié)議,但因需要多方驗證測試可能還需幾年才能投入市場。

歐洲日本政企“迫切追趕”

盡管在全球半導體產(chǎn)業(yè)鏈中占據(jù)極為重要的地位,可歐洲在晶圓制造尤其是先進工藝的實力上并不強。日前,面對美韓等國紛紛強化半導體制造能力,歐洲也再次燃起先進半導體制造的雄心。2021年3月,歐盟委員會發(fā)布了《2030數(shù)字指南針》計劃并提出新的目標,到2030年歐洲先進和可持續(xù)半導體的生產(chǎn)總值至少占全球生產(chǎn)總值的20%,生產(chǎn)能力沖刺2納米。

顯而易見,歐洲半導體研究歷史悠久、產(chǎn)業(yè)鏈各環(huán)節(jié)基礎扎實、科研機構實力強勁。但與強大的設計、研發(fā)實力相比,歐洲在晶圓制造尤其先進工藝上的實力相對薄弱,甚至沒有一家代工企業(yè)入圍全球前十。多年來,英飛凌、恩智浦和意法半導體等企業(yè)專注于汽車電子、工業(yè)產(chǎn)業(yè)等穩(wěn)健領域,但卻錯過了存儲器、晶圓代工和智能手機芯片等需要先進工藝的熱門領域。

目前,隨著汽車智能化、網(wǎng)聯(lián)化深化發(fā)展,芯片在汽車等產(chǎn)業(yè)中發(fā)揮的作用越來越重大,從而使得歐洲發(fā)展先進工藝制造開始變得迫切。以往,由于技術多為傳統(tǒng)特色工藝以及終端客戶多位于亞洲,歐洲半導體企業(yè)更傾向于采取Fablite模式。但這也導致它們并不看好本地化制造,對布局先進工藝制造興趣寥寥。因此,如何將各企業(yè)擰成一股繩將是歐盟的一大難題。

受供應短缺、貿(mào)易摩擦和經(jīng)濟不振等多重因素影響,日本也有意強化本國先進工藝芯片的制造能力。2021年3月,日本政府宣布將出資420億日元,聯(lián)合日本三大半導體廠商——佳能、東京電子以及Screen Semiconductor Solutions共同開發(fā)2nm先進工藝制程。此外,日本官方還推動與臺積電、英特爾等頭部大廠建立合作關系,以尋求收復在全球半導體競賽中的失地。

事實上,日本對先進晶圓制造領域的布局早有跡可循。2020年5月,有關日本政府邀請國外芯片制造商赴日建設晶圓工廠的消息就屢屢傳出,可臺積電后來決定去美國建設先進工藝晶圓代工廠。雖然晶圓制造“外援計劃”落空,但日本仍然沒有放棄,轉而向先進封裝等領域發(fā)起攻勢。最終,臺積電宣布將在東京先進封測廠,并在筑波市設立晶圓及3D封裝研發(fā)中心。

無疑,晶圓制造涉及龐大的資本支出和各項復雜技術。于是,2022年初,日本政府半導體產(chǎn)業(yè)咨詢組官員表示,日本應該提供租稅減免優(yōu)惠,以便在未來十年內達到產(chǎn)能880億美元的投資效益。同時,日本必須在十年內實現(xiàn)2納米制程量產(chǎn)。基于財政優(yōu)惠或補貼、半導體材料領域積累、本土產(chǎn)業(yè)鏈企業(yè)攜手以及外援協(xié)助,日本欲重振芯片制造的長路或將更有底氣。

點評:2納米要過“四道坎”

無論是結構上的創(chuàng)新還是新材料的引入,2納米都將是一個非常關鍵的節(jié)點。原有的多項技術難以滿足發(fā)展要求,產(chǎn)業(yè)界需要從器件架構、工藝變異、熱效應、設備與材料等方面綜合解決。而在這條具備新機遇的賽道上,歐美、日韓等國的企業(yè)均已將芯片制造的突破重點放在2納米上。但想要突破并不容易,2納米芯片制造在架構、材料和設備等方面仍面臨多重瓶頸。

首先,目前2納米制程技術關注的重點在于晶體管架構將由FinFET進入GAAFET世代。相比FinFET,GAAFET架構為四面環(huán)繞式包覆,更能有效提高效能同時控制漏電等,因而或將成為2納米工藝的主流架構。因此,對各企業(yè)而言,熟練掌握GAAFET技術至關重要。但目前,僅有三星在2納米上迭代為第二代GAAFET架構制程,臺積電等廠商仍處在規(guī)劃狀態(tài)。

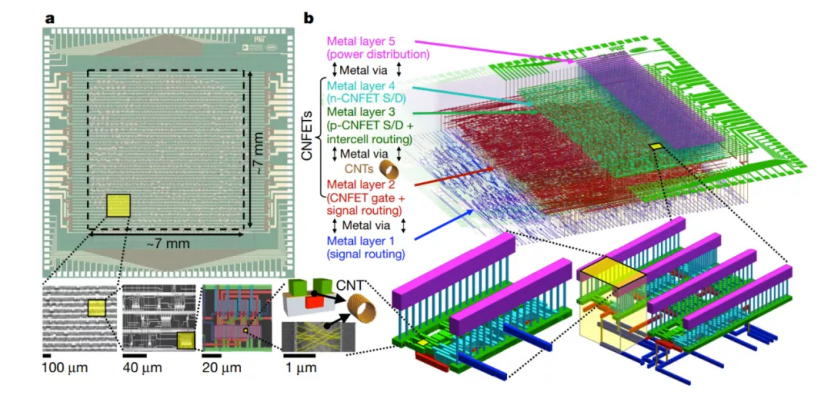

其次,對于2納米工藝研發(fā),新型材料的選擇與應用同樣會起到至關重要的作用。據(jù)了解,二維材料及其范德華異質結電子學器件,已在超低功耗晶體管、超快邏輯運算、光電互聯(lián)及新型高密度存儲等領域表現(xiàn)出極大發(fā)展?jié)摿Γ瑢⒃谖磥碇ν黄?納米以下先進制程研發(fā)。具體而言,石墨烯、碳納米管、過渡金屬化合物等二維或一維材料因尺寸較小有望替代硅基材料。

碳納米管基芯片 圖源:Nature

另外,制造2納米工藝還需要光刻機等設備支撐。據(jù)公開信息,ASML正在研發(fā)High NA(高數(shù)值孔徑)EUV光刻機,可滿足2納米的研發(fā)和生產(chǎn)需求。其首臺High NA EUV光刻機將于2023年開放早期測試,并從2025年開始量產(chǎn)。具體來看,滿足2納米制程生產(chǎn)需求的光刻機,還需要突破革新光學分辨率、光刻膠等相關技術和設備系列問題,因而“道阻且長”。

再者,來自制造成本方面的挑戰(zhàn)更加嚴峻。數(shù)據(jù)顯示,7nm工藝僅研發(fā)費用就至少需要3億美元,5nm工藝平均要5.42億美元,而3nm、2nm的工藝起步價大約在10億美元左右。目前,臺積電3nm工藝的總投資約為500億美元,在建廠方面至少已經(jīng)花費200億美元,可見投入之龐大。如果一旦投入,相關企業(yè)勢必將面臨用戶從哪里來,如何平衡生產(chǎn)成本等問題。

毫無疑問,先進制程技術的推出對于集成電路產(chǎn)業(yè)和市場格局有重大意義,而研發(fā)遲滯的半導體廠商必將被其他廠商的先進制程所超越甚至替代。當前,雖然2納米工藝還有技術架構、材料、設備和成本等不少難點需要克服,但各巨頭的涌入競爭,將可以為整個集成電路行業(yè)和用戶帶來不菲益處。由于工藝技術研發(fā)充滿變數(shù),未來誰能最終脫穎而出還需進一步觀察。(校對/隱德萊希)

本文轉載自集芯網(wǎng),如有侵權,請聯(lián)系刪除!

地址:深圳市龍華區(qū)東環(huán)一路天匯大廈B棟1028室

QQ:2775887586 ? ? ? ? ? TEL:0755-83422736

技術支持:凱鼎電子???粵ICP備16123236號-1